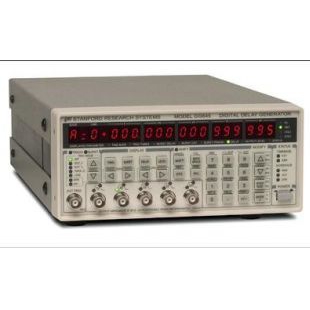

DG645 數字延遲發生器

DG645 是一款多功能數字延遲/脈沖發生器,可以高達 10 MHz 的重復頻率提供精確定義的脈沖。與舊設計相比,該儀器提供了多項改進,包括更低的抖動、更高的精度、更快的觸發速率和更多的輸出。DG645 還具有以太網、GPIB 和 RS-232 接口,用于儀器的計算機或網絡控制。

延遲發生器定時

時序圖 |

所有數字延遲發生器都通過計算快速時鐘(通常為100 MHz)的周期來測量時間間隔。大多數數字延遲發生器還具有較短的可編程模擬延遲,以實現比時鐘周期更精細分辨率的時間間隔。遺憾的是,如果觸發器與時鐘不同相,則可能會出現一個時序不確定的時鐘周期(通常為 10 ns)。

DG645 通過測量觸發器相對于內部時鐘的時序并補償模擬延遲,消除了時序不確定性。這種方法將抖動降低了約100×并允許內部速率發生器以任何速率運行,而不僅僅是時鐘頻率的子倍數。

觸發

DG645 具有多種觸發模式。內部速率發生器的周期抖動小于100 ps,可設置為100 μHz至10 MHz,分辨率為1 μHz。具有可調節閾值和斜率的外部觸發輸入可以觸發定時周期、周期突發或單次觸發。只需按一下鍵即可觸發單次射擊。線路觸發器與交流電源同步運行。后面板觸發YZ輸入可以在定時周期內禁用觸發或任何脈沖輸出。

DG645 通過觸發延遲和預縮放功能支持許多復雜的觸發要求。

觸發器延遲設置連續觸發器之間的最短時間。如果應用程序中的觸發事件生成了顯著的噪聲瞬態,而該噪聲瞬態在生成下一個觸發器之前需要時間衰減,則此功能非常有用。觸發延遲也可用于以輸入觸發速率的次倍數觸發 DG645。

前面板輸出 |

觸發預縮放使 DG645 能夠與更快的信號源同步觸發,但觸發頻率是原始觸發頻率的子倍數。例如,DG645 可以在 1 kHz 下觸發,但通過將觸發輸入預縮放 80,000 與以 80 MHz 運行的鎖模激光器同步。此外,DG645 還為每個前面板輸出包含一個單獨的預分頻器,使每個輸出都能以觸發速率的次倍數運行。

前面板輸出

有五個前面板輸出:T0、AB、CD、EF 和 GH。T型0輸出在定時周期的持續時間內被置位。T的前沿0是零時間參考。編程延遲(A、B、C、D、E、F、G 和 H)設置為 0 s 至 2000 s,分辨率為 5 ps,用于控制四個脈沖輸出的前沿和后沿的時序。

每個前面板輸出可驅動 50 Ω負載,并具有 50 Ω 源阻抗。輸出幅度可在 0.5 V 至 5.0 V 范圍內設置,輸出失調范圍可超過 ±2 VDC,幾乎可以為任何邏輯電平(NIM、ECL、PECL、CMOS 等)供電。在任何輸出幅度下,輸出轉換時間均小于2 ns。

組合輸出 |

后面板輸出

可選的后面板輸出可支持各種應用。選項 1 提供 T0輸出和8個編程延遲(A、B、C、D、E、F、G和H),電壓為5 V邏輯電平,轉換時間小于1 ns。選項2提供相同的輸出,但為30 V、100 ns脈沖,轉換時間小于5 ns,用于高噪聲環境中的時序分配。選項3提供8個組合輸出,在5 V邏輯電平下提供1至4個脈沖,轉換時間小于1 ns。每個輸出具有50 Ω源阻抗。

時基

標準時基的精度為 5 ppm,抖動10-8,適用于多種應用。可選的時基適用于需要更高速率和延遲精度或降低速率和延遲抖動的用戶。

對于標準時基,1 s 延遲的定時誤差可能高達 5 μs,OCXO 時基為 200 ns,但對于銣時基,時序誤差僅為 500 ps(校準后均為一年)。

時序誤差與延遲 |

對于短延遲,抖動通常為 20 ps。但是,對于 1 秒的延遲,標準時基可產生高達 10 ns 的抖動,而可選時基可產生不到 10 ps 的額外抖動。

快速上升時間模塊

DG645 前面板輸出的轉換時間小于 2 ns。SRD1 是一種內置于直插式 BNC 連接器中的附件,可將前面板輸出的上升時間縮短到 100 ps 以下。最多可將 5 個 SRD1 連接到前面板,以縮短所有輸出的上升時間。

抖動與延遲 |